1 Introduction

Digital video captures external image information using a video capture device such as a camera and digitizes the image information, and then records it to a storage medium (such as a video tape, hard disk, optical disk) or transmits it over a network. Video surveillance is of great importance in security systems. A portable multimedia video monitor based on the TMS320DM355 DaVinci Digital Media System-on-Chip (DMSoC) is proposed here.

2 DaVinci Technology Brief

DaVinci technology is TI's complete solution for digital video image processing and applications, including processors, development tools, software and system expertise. DaVinci technology optimizes and processes digital video with digital signal processing and integrated circuit technology to provide highly integrated system-on-a-chip (SoC). The system-on-chip has efficient processing power, memory, and I/O bandwidth. It is also a balanced internal interconnect and dedicated peripheral combination. The hardware and software of the digital video subsystem integrates a configurable and programmable development toolset. DaVinci technology enables developers to get rid of the technical details of digital video. The entire DaVinci software architecture covers low-level OS drivers and APIs. Easy to implement digital video capabilities. Developers don't need to understand the various mechanisms behind audio, video, video, and voice CODECs and DSP programming. They only need to call a small number of functions to provide codec and video capabilities. DaVinci technology reduces the complexity of the many components that systems create and manage by providing an open platform. On this platform, Tl and its third-party partners integrate the various components required to form a digital video system, all based on the DaVinci platform. At the same time, the open development platform is also extended to the application, and the implementation application is also based on the same DaVinci platform.

At present, TI's devices using Davinci technology are mainly divided into three categories: 1ARM926EJ+MJCP (MPEG4 and JPEG coprocessor MPEG4/JPEG), typical device TMS320DM355; 2 TMs320C6000 series DSP TMS320DM643 1/33/35/37 and TMS320DM647/ 8;3 DSP TMS320DM6446/43/41 by ARM926EJ+TMS320C6000 series, including TMS320DM6446/41 also includes video image coprocessor VICP. Table 1 gives a comparison of TI's DaVinci technology devices.

3 Introduction to TMS320DM355

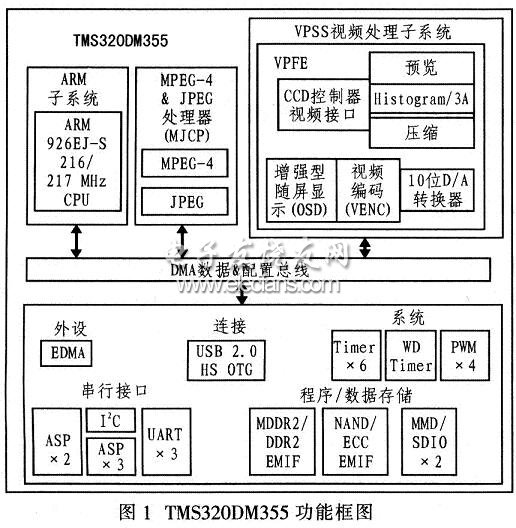

The high-performance, low-power TMS32DM355 DaVinci technology device uses the coprocessor MJCP to implement multimedia data encoding and decoding due to the internal multimedia processor without DSP core. Therefore, the TMS320DM355 can achieve a low power, low cost design. The TMS320DM355 consumes approximately 400 mW of HD MPEG-4 encoding while standby power consumption is only 1 mW. Using a TMS320DM355-based digital camera in video mode, two AA batteries can record up to 80 minutes of HD video, doubling the battery life of HD products. TMS320DM355 internal integrated video processing subsystem VPSS (Video Processing Subsvrs-tem), MPEG-4/JPEG coprocessor (MJCP), ARM926EJ-S core and a variety of peripherals, can be applied to digital cameras, IP cameras, digital Photo frames, medical imaging and baby video monitors. Figure 1 shows the internal functional block diagram of the TMS320DM355.

The TMS320DM355 includes a Harvard architecture ARM core: ARM926EJ-S processor supports ARM extended DSP instructions and Jazelle technology, 32 KBRAM, 8 KB ROM, 16 KB I-cache, 8 KB D-cache; it can handle 16/32-bit instructions And 8/16/32 bit data. It enhances the architecture by using the coprocessor CPl5 and protection modules and provides a data and program memory management unit MMU. The MMU has two 64-bit translation bypass buffers, TLB, for storing instructions and data streams, each of which maps memory segments and size pages. In order to ensure access to instructions and data during the kernel cycle, a separate 16 Kbyte instruction cache and 8 Kbyte data cache are provided, and the instruction and data cache are connected via VIVT4. In addition, the device has a write buffer that boosts core performance with a buffered data capacity of up to 17 words.

A dedicated video image processor is used to process the video data: the video processing subsystem VPSS includes a video front end input interface VPFE and a video end VPBE output interface, and the video front end input interface is used to receive input image information of an external sensor or video decoder, video The end output interface outputs images to the SDTV, LCD, HDTV and other display screens. The video front-end input (VPFE) interface is composed of a CCD controller, a hardware image signal processor, an image channel IP-IPE module, an automatic exposure/white balance/focus module H3A, and a register. The CCD controller can be connected to a video decoder, CMOS sensor or charge coupled device; IPIPE is a real-time hardware graphics processor for real-time image processing that converts raw graphics from CMOS/CCD to the International Telecommunication Union ITU Digital Video Standard BT. 60I/BT. The 656's 8/16 digit YCbCr 4:2:2; H3A module provides raw graphics information.

The Video End Output (VPBE) interface consists of an online video display processor/screen control system OSD and a compatible NTSC/PAL video output encoder VENC. The online video display processor can display 2 separate video windows or 2 separate OSD windows. It can also be displayed in the form of a video window, an OSD window, and a property window. The video decoder is at 54. The rate of MHz is D/A converted to provide video or audio output in NTSC/PA L, S and other formats. At the same time, the device also has 8/16-bit YCC to 18-bit RGB666 digital output; ITU Digital Video Standard BT. 601/BT. 656's 8/16-bit digital YCbCr 4:2:2 interface: The output also supports an interface to the digital HDTV HDTV (720p/1080i) extended encoder. The cache logic is connected to the DDR2/mDDR on-chip controller of the TMS320DM355 to facilitate access to the memory, and store image information collected by the camera and processed by the VPFE to the memory, so that the stored image information can be output to the display device through the VPBE.

For digital image processing, the MPEG4 and JPEG hardware coprocessor MJCP (MPEG4/JPEGG Coprocessor) provides high-definition MPEG4-SP codec in 720p format and 30 frames/s, and is available at 50 megapixels per second. JPEG codec function. In terms of storage, the extended memory interface EMIF includes one 8/16-bit and one 16-bit mDDR/DDR2, and the expandable memory types are mDDR, DDR2, SDRAM, OneNAND, NANDFlash, SM/xD, etc.; other on-chip peripheral extension control The device also includes: 2 MMC (MulTImedia Card)/SD (Secure·Digital) interface; 2 audio interface ASP (Audio Serial Port) interface controller, supports AC97 audio coding interface, 12S interface form: 1 master/slave I2C (Inter-Integrated Circui) interface controller: 1 USB 2. OTG interface controller: 1 configurable video-specific input and output ports.

Stainless Steel Screw, Stainless Steel Open Eye Hook Screw, Stainless Steel Drywalll Screw

ShenZhen Haofa Metal Precision Parts Technology Co., Ltd. , https://www.haofametal.com